New Batch Starts In a Week

Synthesis and STA Training is a 4 months course, provides the participants with in depth exposure to both Synthesis and complete Timing SignOff strategies for successful and confident Tape-Out of the Design to the Semiconductor Fabrication House.

Next Batch

1-1 Dedicated Mentor Support

24/7 Tool Access

Multiple Mock Interviews

Industry Standard Projects

Support with Resume Update

Synthesis and STA Training Overview

Synthesis and STA Training is a 4 months course, provides the participants with in-depth exposure to both Synthesis and complete Timing SignOff strategies for successful and confident Tape-Out of the Design to the Semiconductor Fabrication House. STA Training: Timing is the heartbeat of any chip. Thorough understanding of timing concepts and development of timing constraints are given through this STA Training, especially when it comes to Ultra Deep Sub-Micron Technologies such as 28nm to 5nm. There are multiple parameters that decide how the timing of a chip would be functioning, like Transition times of Clock phases and Data Path signals, Process and Voltage and Temperature (PVT) variations, Crosstalk noise affecting functionality of the chip, Crosstalk Delay affecting timing of the chip—which will be covered in greater detail in this STA Training. Other topics such as Advanced OCV, requirement of Clock path tweaking to meet desired frequency of the chip will be discussed extensively. Pessimism inclusion when design is tapped-out has been a norm to avoid any Silicon surprises, but for higher frequency designs on lower technology nodes, pessimism beyond a limit could be an over-do—in which case pessimism-Removal is done through Path-Based Analysis rather than Graph based Analysis. This topic is covered with fine clarity in this STA Training. Above all, the fundamental part of setup and hold time fixing covering the above points are the key aspects of this STA Training. Candidates will get access to tools both at the institute and have the option to connect to servers from home using Secure VPN to work on new Sign Off projects hands-on. Fixing of timing violations based on Sign-Off analysis for Multi Mode Multi Corner through ECOs would be across the breadth of this STA Training. Objective of this STA training is to shape graduating Bachelor’s and Master’s degree students as well as Physical Design Engineers to explore opportunities in Block Level as well as Full Chip STA. Synthesis Training: Synthesis training includes all the aspects starting from HDL modelling, Synthesis flow, Constraints, analysing and debugging the results, optimization techniques, report generation and hands-on projects to understand the Synthesis complete flow. Below are the STA Training topics. SignOff STA Training topics : - Fundamental Setup and Hold Timing Checks - Timing Arcs across Design Instances - Stage Delay covering Cell Delay and Net Delay - Asynchronous Flop, recovery and removal checks - Cross Clock Timing Analysis - Interface Timing Analysis (between reg and IO) - Clock group based timing analysis - Crosstalk Delay and Crosstalk Noise - Advanced On Chip Variation, CPPR - Multi-Mode Multi-Corner timing analysis - Graph Based and Path based analysis - Timing DRC – Transition, Capacitance, Fanout fixes. - Clock path ECO and Data path ECO - Constraint Development specifically Interface timing Synthesis Training covers the aspect of converting the design in the form of RTL into Technology mapped netlist. Synthesis is an algorithm-intensive task consisting of many stages within it requiring various inputs in order to produce a functionally correct netlist. The main part of Synthesis Training consists of reading in the design, converting RTL to Boolean equations through elaboration, then converting the Boolean equations to Generic Mapped Cells and then technology mapped cells from library, setting constraints, optimizing the design, analyzing the results and saving the design database for Placement and Routing stage to take on. Candidates who are interested in exploring opportunities in Synthesis and Front-end STA can undergo this in-depth Synthesis training to get good understanding of RTL constructs, Gate level Netlist, Constraint Development, Latch based designs, pipe lining and re-timing, basic Scan stitching, Setup timing closure, Topography based logic restructuring, Wire Load Models, Logical Equivalence Checks. Hierarchical Synthesis is another key feature covered in this Synthesis Training. Cadence Implementation Suite for Synthesis (as RTL Compiler / Genus) would be used in this Synthesis Training program. Candidates would get hands-on work on two full designs. Synthesis Training Topics covered: - Introduction to synthesis - Reading RTL in HDL form, dotlibs, SDC - Different types of RTL constructs - Analyzing dotlib files - Elaboration and Generic Synthesis - Understanding DesignWare components and Logical Operators - Clock gating insertion for reducing Dynamic power post CTS - Creating list of dont_touch and dont_use cells - Technology mapped Synthesis and optimization - Scan Insertion techniques - Checking Design for number of instances, area estimate - Check clock reaching clock pins of flops, unblocked flops - Time borrowing concepts for latch based paths - Leakage variants of standard cells LVT, RVT, HVT - Constraints on logical hierarchy boundaries - Setting Max Transition, Max Capacitance, Max Fanout - Push down and pull up timing constraints - Master clocks and generated clocks in design - Estimating uncertainty values, input and output delays in SDC - False path, Multi cycle path exceptions. - Disabling timing loops in design - Logical Equivalence Checking fundamentals (Top level and Hierarchical) - Hand off database to PnR

Design Compiler and Primetime

Import design

Understanding Liberty file

Synthesis flow

Writing Synopsys design constraints file

Multi voltage design and UPF

Physical aware synthesis

Synthesis optimization techniques

Synthesis hands on using tool dc shell

Latency , skew and timing paths

Setup Violation

Hold Violation

In_to_reg paths

reg_to_out paths

Derate and its Types

Derate Overview

PVT and MCMM

PVT Corners

MCMM Concepts

Writing MCMM File

Special Timing Paths

Multicycle Path

Half Cycle Path

Clock Domain Crossing (CDC)

Recovery and Removal Checks

Synchronizers

Path Grouping

Useful Skew

Clock Push and Clock Pull

Time Borrowing

Cross Talk Effects

Cross Talk Noise

Cross Talk Delay

Design Analysis Tools

Design Analysis using ICC2 or Fusion Compiler (FC)

SPEF Extraction using StarRC

PrimeTime Lab

Input for PrimeTime

Analysis Coverage

Check Timing

Cross-talk Analysis

Timing Fixing Methods

Physical Aware ECO

PrimeTime DMSA Flow

Key Features

Who All Can Attend This Synthesis and STA Training?

This course is for recent engineering graduates and experienced physical design engineers wanting to master synthesis and static timing analysis for successful chip implementation in the VLSI industry.Pre-requisites To Take Synthesis and STA Training

- Basic understanding of digital design concepts and RTL.

- Familiarity with Verilog or VHDL hardware description languages.

- Exposure to basic VLSI design flow concepts.

High Demand for Synthesis and STA Training

Know about the Growing VLSI industry

Physical Design Engineers are crucial in the semiconductor industry, responsible for the physical implementation of integrated circuits. The demand for these engineers is consistently high, with a projected growth of approximately 7-10% annually in the VLSI sector in India. They translate logical designs into physical layouts, ensuring timing, power, and area constraints are met for manufacturability.

₹4LPA

₹6 LPA

₹8 LPA

₹15 LPA

₹20+ LPA

- Customized training programs for teams

- Upskill and reskill employees with industry-relevant content

- Interactive sessions led by expert trainers

- Hands-on projects and real-world case studies

- Flexible delivery in online

- Improve productivity and efficiency

- Access to training resources and material

- Learn in real-time with instructor-led sessions

- Flexible access from anywhere

- Recorded sessions available for revision

- Training on industry-standard tools

- Get certification after completion

- Self-paced learning as per your flexibility

- Industry-aligned learning modules

- Certification after course completion

- Access to structured video lessons and materials

- Track your progress step by step

- Access to learning materials for more than 1.5 years

This 4-month Synthesis and STA Training is essential for mastering the critical steps of converting RTL to a technology-mapped netlist and ensuring timing closure for successful chip tape-out. It provides in-depth knowledge of timing concepts for advanced technology nodes (28nm-5nm), covering PVT variations, crosstalk, advanced OCV, and pessimism removal. Hands-on projects and tool access solidify these vital skills for the semiconductor industry.

Career Path

Learning Path

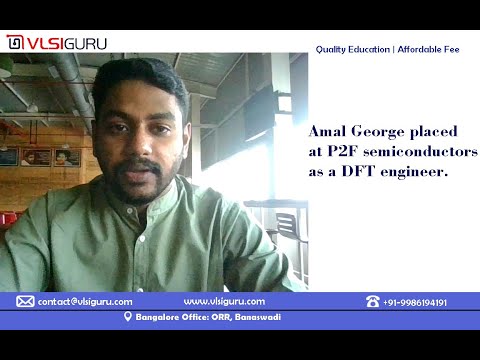

At VLSIGuru, we believe that education should lead to meaningful employment. Our training programs are designed not just to impart technical excellence, but also to bridge the gap between academic learning and industry demands. With a strong network of hiring partners and a proven track record, we ensure that our students are career-ready.

Placement Highlights

- Industry-aligned curriculum

- Hands-on projects and case studies

- Communication skills

- Resume building and interview preparation

- Technical and HR mock sessions

- Aptitude and domain-specific test series

- Regular drives and exclusive hiring events with partner companies

- Resume building and interview preparation

At VLSIGURU, we provide industry-focused VLSI training and guidance that helps students and professionals build strong technical skills and succeed in their careers. Our programs are designed to be practical, flexible, and aligned with current industry requirements.

Student Reviews

Frequently Asked Questions

- Course presentations for all topics

- Session notes

- Lab documents with detailed steps

- User guides

- Expertise on Advanced Digital design concepts

- Course will involve practical exposure to Synthesis and STA with 2 hands-on projects. Every session will have theory with supporting labs.

Each session of course is recorded, missed session videos will be shared

- Yes, You will have option to view the recorded videos of course for the sessions missed

- You will have option to repeat the course any time in next 1 year

Yes, Course fee also includes support for doubt clarification sessions even after course completion

You have option to mail you queries

Option to meet in person to clarify doubts

This training will enhance your skill set, making you more valuable in your current role and opening doors to advanced career opportunities in VLSI.

Professionals with these skills typically command competitive salaries, with ranges varying based on experience, location, and company size.

Yes, our curriculum is continuously updated to reflect the latest industry standards and address the growing demand for skilled Synthesis and STA engineers.

You can pursue roles like Synthesis Engineer, Static Timing Analysis Engineer, DFT Engineer, and contribute significantly to SoC development.

There is a significant and growing demand for skilled Synthesis and STA engineers in the semiconductor industry.

The field offers excellent future prospects with continuous innovation and increasing complexity in VLSI design, ensuring long-term career growth.

The average salary for a Synthesis Engineer in India can range from ₹4 Lakhs to ₹15 Lakhs per annum, depending on experience and company.

Similarly, an STA Engineer in India can expect an average salary in the range of ₹4.5 Lakhs to ₹18 Lakhs per annum, influenced by experience and employer.

Yes, experience is a significant factor influencing salary expectations for both Synthesis and STA engineers, with more experienced professionals earning higher compensation.

Synthesis translates RTL code into a gate-level netlist, while STA verifies the timing performance of that netlist, ensuring correct operation.

Yes, you will receive a recognized certificate that validates your expertise in Synthesis and STA.

Absolutely, the course includes crucial aspects of low-power design techniques in both synthesis and static timing analysis.

The course offers a comprehensive understanding, taking you from foundational concepts to an advanced level of practical application.