New Batch Starts In a Week

DDR is an essential component of every complex SOC. It requires every engineer working on SoC to be well versed with DDR protocol concepts including DDR controller, DDR PHY, DDR memory, etc.

Next Batch

1-1 Dedicated Mentor Support

24/7 Tool Access

Multiple Mock Interviews

Industry Standard Projects

Support with Resume Update

DDR5 Training Overview

Course Overview

DDR5 protocol training is focused on understanding of all the aspects of DDR5 including DDR5 ports, commands, timing diagrams, training sequences, post package repair, ODT etc.

Functional Description

DDR5 Pinout Assignments

DDR5 Addressing

Reset and Initialization Procedure

Mode Registers

Command Description and Operation

2-Cycle Command Cancel

MULTI-PURPOSE Command (MPC)

2N Mode

CS Geardown Mode

ACTIVATE Command

PRECHARGE Command

IO Features and Modes

Programmable Preamble and Postamble

Interamble

On-Die ECC

Write Operations

READ Operations

Temperature Sensor

REFRESH Operation

Self Refresh Operation

Input Clock Frequency Change

Power-Down Mode

Maximum Power Saving Mode

Connectivity Test Mode

ZQ Calibration Commands

Per-DRAM Addressability

CS Training Mode

CA Training Mode

Write Leveling (WL) Training Mode

Read Training Pattern

Read Preamble Training Mode

Post Package Repair

Memory BIST Post Package Repair (mPPR)

On-Die Termination

Key Features

Who All Can Attend This DDR5 Training?

This DDR5 Training is designed for professionals looking to specialize in next-generation memory technologies, focusing on DDR5 architecture, interface design, and validation techniques. It's ideal for engineers involved in high-speed memory systems and SoC integration.Pre-requisites To Take DDR5 Training

- Exposure to basic memory concepts like SRAM, FLash, etc

- Exposure to digital design concepts

High Demand for DDR5 Training

Know about the Growing VLSI industry

Protocol Design Engineers are responsible for defining and implementing USB4 protocol stacks and ensuring compliance with USB4 specifications.

With USB4 adoption rapidly growing across consumer and enterprise devices, there’s an increasing demand for engineers who can design robust, high-speed serial protocols.

Companies like Intel, AMD, Qualcomm, and Synopsys actively hire for this profile.

₹6 LPA

₹10 LPA

₹16 LPA

₹22 LPA

₹30+ LPA

- Customized training programs for teams

- Upskill and reskill employees with industry-relevant content

- Interactive sessions led by expert trainers

- Hands-on projects and real-world case studies

- Flexible delivery in online

- Improve productivity and efficiency

- Access to training resources and material

- Learn in real-time with instructor-led sessions

- Flexible access from anywhere

- Recorded sessions available for revision

- Training on industry-standard tools

- Get certification after completion

- Self-paced learning as per your flexibility

- Industry-aligned learning modules

- Certification after course completion

- Access to structured video lessons and materials

- Track your progress step by step

- Access to learning materials for more than 1.5 years

DDR5 protocol training provides a comprehensive understanding of all DDR5 aspects, from ports and commands to intricate timing diagrams and essential training sequences. Mastering post-package repair and ODT techniques is crucial for next-generation high-performance systems. This knowledge empowers you to effectively design, verify, and troubleshoot cutting-edge memory interfaces, making you a highly sought-after professional in the VLSI domain.

Career Path

Learning Path

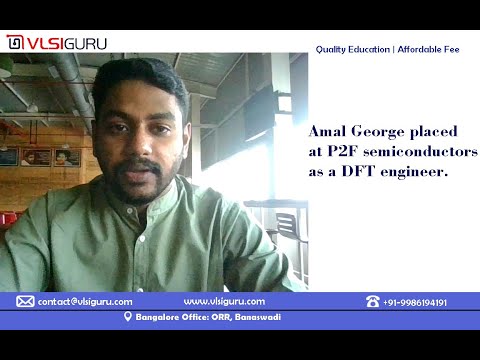

At VLSIGuru, we believe that education should lead to meaningful employment. Our training programs are designed not just to impart technical excellence, but also to bridge the gap between academic learning and industry demands. With a strong network of hiring partners and a proven track record, we ensure that our students are career-ready.

Placement Highlights

- Industry-aligned curriculum

- Hands-on projects and case studies

- Communication skills

- Resume building and interview preparation

- Technical and HR mock sessions

- Aptitude and domain-specific test series

- Regular drives and exclusive hiring events with partner companies

- Resume building and interview preparation

At VLSIGURU, we provide industry-focused VLSI training and guidance that helps students and professionals build strong technical skills and succeed in their careers. Our programs are designed to be practical, flexible, and aligned with current industry requirements.

Student Reviews

Frequently Asked Questions

- Course presentations for all topics

- Session notes

- Lab documents with detailed steps

- User guides

- Exposure to basic memory concepts like SRAM, Flash, etc

- Exposure to digital design concepts

Dedicated sessions planned to train student on Protocol specific TB component Coding

Each session of course is recorded, missed session videos will be shared

- Yes, You will have option to view the recorded videos of course for the sessions missed.

- You will have option to repeat the course any time in next 1 year.

- Yes, Course fee also includes support for doubt clarification sessions even after course completion.

- You have option to mail you queries.

- Option to meet in person to clarify doubts

DDR5 signifies "Double Data Rate 5th generation," the latest evolution in high-speed memory technology. Our course will delve into how this advancement unlocks significant performance gains for modern systems.

The core benefit is substantially higher bandwidth, enabling faster data transfer and improved system responsiveness. VLSI Guru's training will equip you with the skills to leverage this increased performance in your designs.

DDR5 boasts innovations like On-Die ECC for enhanced reliability and Decision Feedback Equalization (DFE) for signal integrity at high speeds. Understanding these features, which we cover extensively, is crucial for next-gen VLSI.

On-Die Error Correcting Code integrated directly within the DRAM chip significantly improves data integrity and system stability. Our course will explain how this crucial feature impacts your VLSI design and verification workflows.

DFE is a vital signaling technique that enhances signal clarity at the higher operating frequencies of DDR5, ensuring reliable data transmission. VLSI Guru's practical sessions will demonstrate how DFE is critical for high-performance memory interfaces.

DDR5 typically operates at a lower 1.1V, contributing to improved power efficiency in modern systems. Our training will highlight the power-saving aspects and their implications for your VLSI designs.

DDR5 introduces a dual-channel architecture with two independent 40-bit subchannels per module, enhancing data transfer parallelism. VLSI Guru will provide a deep dive into this architecture for optimized memory controller design and verification.

The standard burst length in DDR5 is typically 16 (BL16), influencing data access granularity and efficiency. Our course will cover how burst length affects memory controller design and overall system performance.

High-performance computing, data centers, AI/ML accelerators, and advanced gaming platforms are prime beneficiaries of DDR5's capabilities. Mastering DDR5 with VLSI Guru opens doors to designing for these cutting-edge applications.

The Memory Controller is the crucial interface that manages all data transfers between the system and DDR5 memory. Our training will equip you with in-depth knowledge of designing and verifying efficient DDR5 memory controllers.

JEDEC standards ensure interoperability and consistent performance across different DDR5 memory and controller vendors. VLSI Guru's curriculum emphasizes adherence to these standards for robust and reliable designs.

Higher density DDR5 modules enable larger memory capacities in systems without increasing the number of physical slots. Our course will explore the design and verification challenges associated with these high-capacity modules.

DDR5 achieves better power efficiency through lower operating voltage and intelligent power management features. Understanding these advancements, which we cover in detail, is vital for designing energy-conscious VLSI systems.

DDR5 modules come in various speed grades (e.g., DDR5-4800, DDR5-6400 and beyond), offering flexibility for different performance requirements. VLSI Guru will guide you in selecting and verifying the appropriate speed grades for your applications.